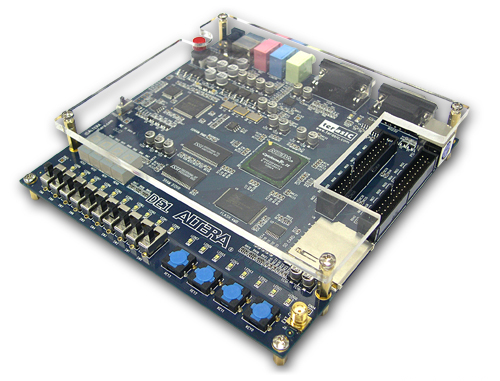

Hello there, today I will introduce you my brand new Altera DE1 FPGA Development Board.

Yeah! This board substitutes my Xilinx Spartan 3AN for a while, due to difficults in RAM usage (DDR2) of this board and lacking for other features (decent audio DAC, SRAM, SD slot,...).

Altera DE1 has many good and interesting features like:

- Cyclone II EP2C20F484C7 (18,752 Logic Elements, 52x M4K 4kbits ram blocks, 234kbits embedded memory, 26x 18-bit x 18-bit multipliers, 4 PLL, 315 I/O pins)

- EPCS4 4-Mbit serial configuration device programmable to store the FPGA configuration autoloaded on start

- 512KByte SRAM (256x16bit asynchronous, very very useful and simple to program)

- 8MB DRAM (synchronous DRAM but not hard-to-use as DDR2 one)

- 4MB Flash RAM

- 1x 50Mhz Clock

- 1x 27Mhz Clock

- 1x External SMA clock input

- 12bit VGA DAC (4096 colors on screen is enough for many things)

- 24bit Audio CODEC with lin-out, line-in, mic-in connectors (wow! how many beautiful things can we do with a similar audio DAC!!!)

- Onboard SD card slot (yeah! useful to access external data like... ROMS....)

- PS/2 keyboard connector

- 10 red LEDs, 8 green LEDs, 10 switches

- 4x debounced pushbuttons

- 4x 7-segments display

- 2x IDE expansion headers to accessing external devices/resources

- 1x RS-232 (useful to monitor/debug application from PC)