It's time to think about the SC-3000X enclosure...

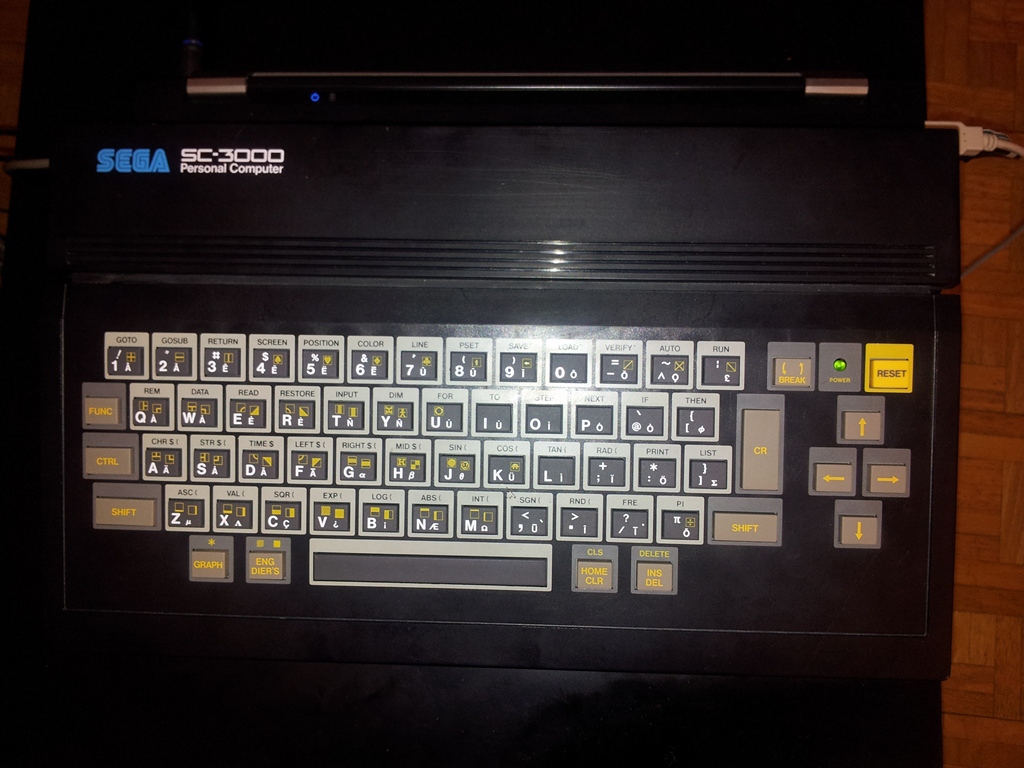

The original SC-3000? Uh?

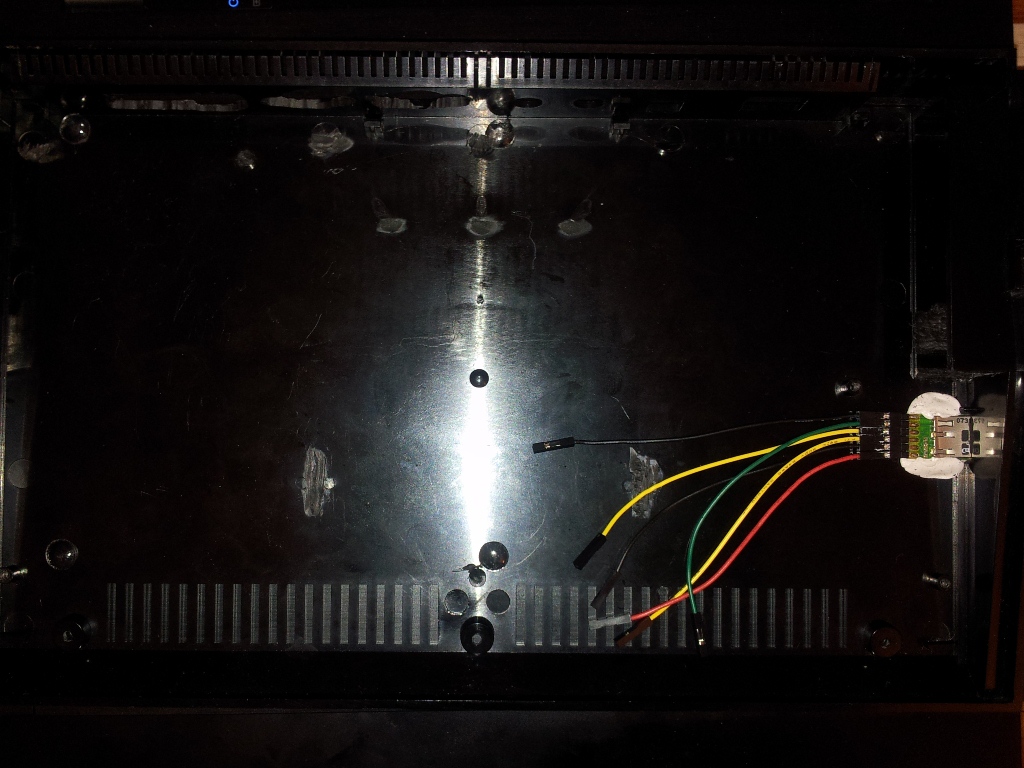

Inside view. Original mobo removed, flatten space, my Dremel does the job! Trioflex microSD card adapter present on right, fixed on plastic with UHU Patafix (needed some final solution).

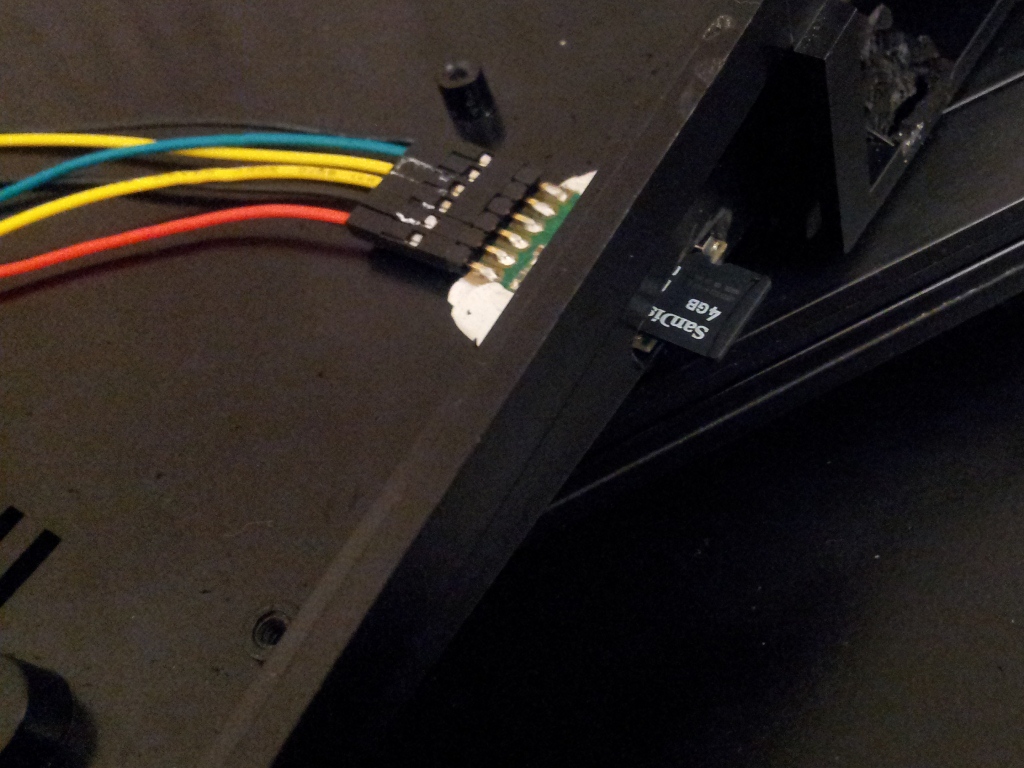

Detail of microSD adapter with microSD inside (4GB).

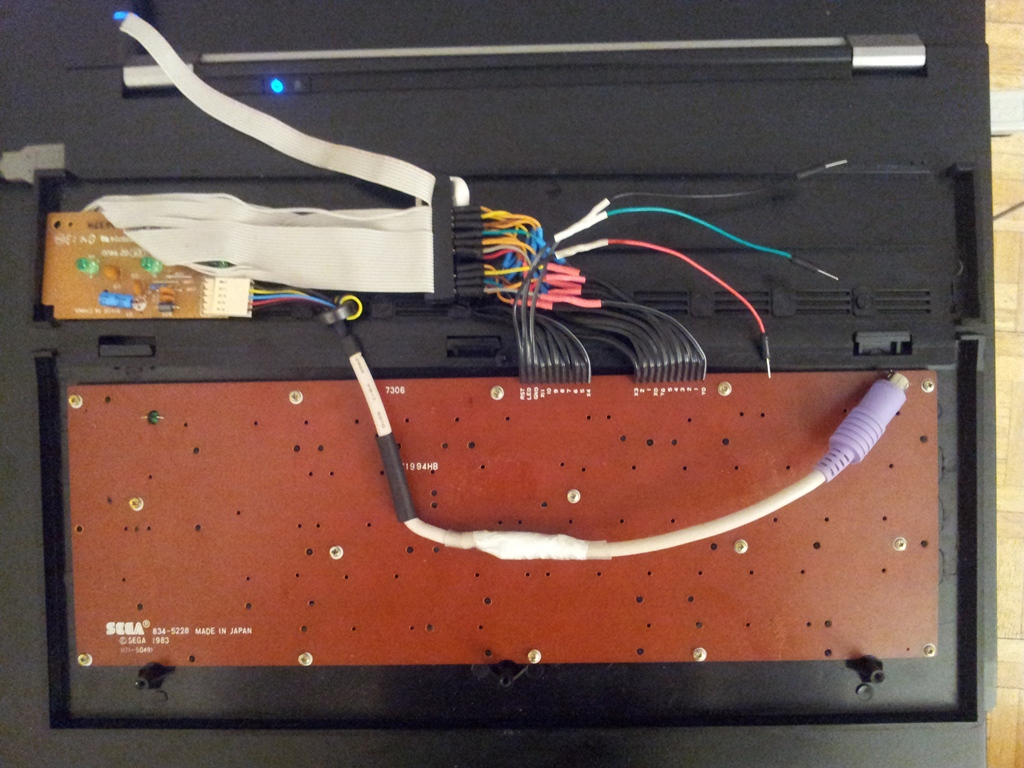

Original keyboard connected (through floppy cable) to PS/2 controller card got from an old PC keyboard. Total remap of keys was done!

Right view of modified enclosure.